Running 32-bit RISC-V Linux with Octa-core SMP in LiteX/VexRiscv on Qmtech Wukong Board

We have succeeded in configuring an SoC with octa-core + FPU + AES using LiteX/VexRiscv, and running 32-bit RISC-V Linux on the Wukong board, one of the Qmtech’s FPGA boards.

We also configured an SoC with dual-core + FPU + AES to run 32-bit Linux on the Digilent’s Arty A7-35.

These systems are based on github.com/litex-hub/linux-on-litex-vexriscv.

VexRiscv

The VexRiscv is an open source 32-bit RISC-V softcore written in a hardware description language called SpinalHDL.

The VexRiscv can be extended with plugins.

The AES (Advanced Encryption Standard) plug-in was added in December 2020, and the FPU (Floating Point Unit) plug-in was added in March 2021.

LiteX

LiteX consists of an open source SoC (System on Chip) builder written in Migen, a Python DSL (Domain Specific Language), and library of IP components.

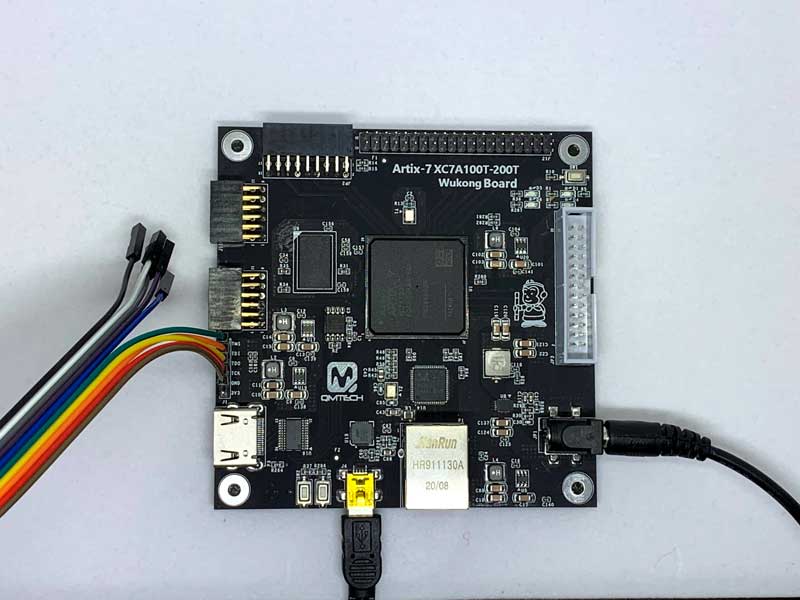

Qmtech Wukong Board

Wukong board is one of the Qmtech’s FPGA (Field-Programmable Gate Array) board using the Xilinx’s Artix-7.

The previous board was equipped with an HDMI display interface, GMII Ethernet interface, USB-UART, etc.

The current board has been added one microSD card slot, and the XC7A200T model can be selected.

We are currently using the XC7A100T model.

Summary

We use LiteX, which consists of an SoC builder and library of IP components, and VexRiscv, an open source 32-bit RISC-V softcore that can be extended by plugins.

We have successfully configured SoCs for each of the Qmtech’s Wukong board and the Digilent’s Arty A7-35 to fit the size of the FPGA and run 32-bit Linux.