Running 64-bit RISC-V Linux in LiteX/Rocket on Arty A7-35T

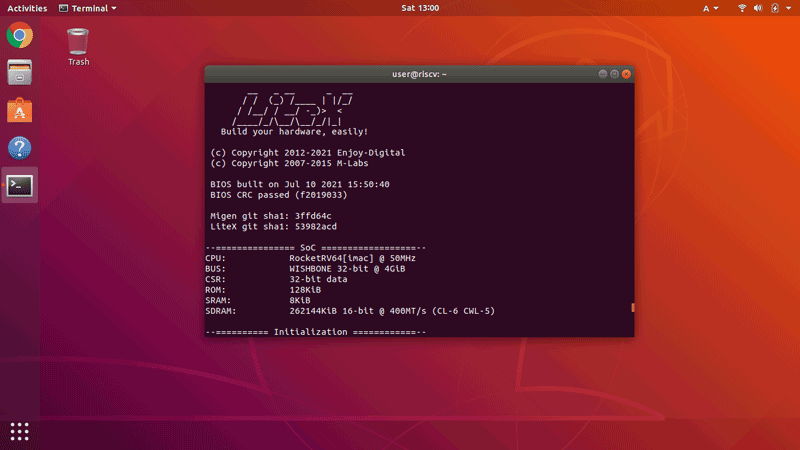

We have succeeded in configuring an SoC using the LiteX/Rocket, and running 64-bit RISC-V Linux on the Arty A7-35T from Digilent.

It was also successful with the Qmtech’s Wukong board.

These systems are based on github.com/litex-hub/linux-on-litex-rocket.

Rocket

The Rocket is an open source RISC-V softcore written in Chisel, a hardware description language.

The Rocket core is a 5-stage in-order core with 64-bit RISC-V (RV64) and 32-bit RISC-V (RV32) configurations.

In addition, the Rocket core configuration for RV64 includes Big/Med/Small/Tiny.

LiteX/Rocket

The LiteX consists of an open source System on Chip (SoC) builder and library of Intellectual Property (IP) components.

To use the Rocket with the LiteX, you need to clone github.com/litex-hub/pythondata-cpu-rocket that contains files converted form Chisel to Verilog, not the Rocket Chip Generator environment.

Digilent Arty A7

The Arty A7 is a Field-Programmable Gate Array (FPGA) board from Digilent.

This board features the Xilinx’s FPGA Artix-7.

The main specifications of the board are as follows.

- FPGA: XC7A35T/XC7A100T

- RAM: 256MB

- MII Ethernet

- USB-UART bridge

- Pmod interface: 4

There are two variants of the Arty A7: The Arty A7-35T features the XC7A35T, and the Arty A7-100T features the larger XC7A100T.

We are currently using the Arty A7-35T.

When configuring an SoC for the LiteX/Rocket on the Arty A7-35T, it is not possible to support both SDcard (Pmod MicroSD) and Ethernet due to the small size of the FPGA.

For this reason, we have created gateware that supports each of SDcard and Ethernet, and use them according to the purpose.

Summary

We have successfully configured SoCs for each of the Digilent’s Arty A7-35T and the Qmtech’s Wukong board to fit the size of the FPGA using the LiteX/Rocket, and run 64-bit Linux.