Running Dual-Core RISC-V Linux on Cheap FPGA Board

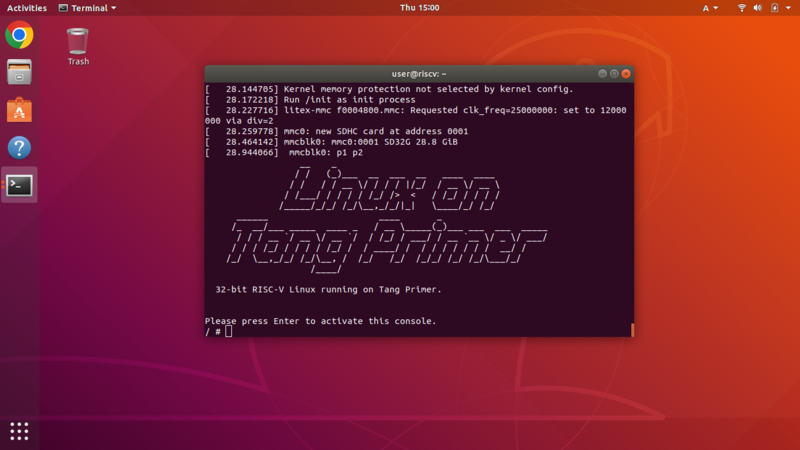

We have successfully built a dual-core 32-bit RISC-V SoC for a Sipeed Tang Primer that we purchased for about $20 and run Linux.

In addition to the above RV32IMAC dual-core SoC, we have also successfully run Linux on the RV32IMAFDC single-core SoC that supports single-precision and double-precision floating point extensions.

Click here for related articles.

- Porting PicoSoC with PicoRV32 to Sipeed Tang Primer

- Testing LiteX/VexRiscv on Sipeed Tang Primer

- Running Dual-Core RISC-V Linux on Cheap FPGA Board (this article)

Sipeed Tang Primer

Sipeed’s Tang Primer is an inexpensive FPGA board using Anlogic’s FPGA EG4S20BG256. We bought this board for about $20, but it seems to be discontinued.

Tang Primer has an FPGA with 20k LUTs and can run a RISC-V CPU as introduced in previous articles.

Main Issues to Run RISC-V Linux on Tang Primer

The main issues to run Linux on Tang Primer using SoC builder LiteX are as follows.

- Gateware

- 8MiB SDRAM support

- CPU configuration change

- MicroSD card support

- Software

- Linux kernel size reduction

- OpenSBI configuration change

Since Tang Primer only has about 130KiB of SRAM, adding support for 8MiB SDRAM and reducing the size of the Linux kernel was absolutely necessary.

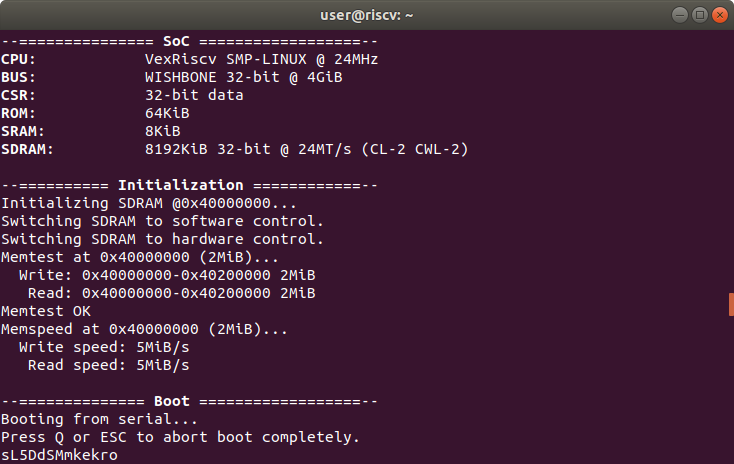

Linux Capable SoC for Tang Primer

The main specifications of the dual-core SoC are as follows.

- CPU: Dual-core 32-bit RISC-V

- ISA: RV32IMAC

- Operating frequency: 24 MHz

- SDRAM: 8 MiB

- ROM: 64 KiB

- UART: 1 channel

- MicroSD card support

For single-core SoC, only the CPU specifications change as follows.

- CPU: Single-core 32-bit RISC-V

- ISA: RV32IMAFDC (RV32GC)

Note: VexRiscv for LiteX is used for CPU.

RISC-V Linux on Tang Primer

Featured image is the login screen when using BusyBox as rootfs.

The output of cat /proc/cpuinfo on the dual-core SoC is as follows, and two cores are recognized.

/ # cat /proc/cpuinfo processor : 0 hart : 0 isa : rv32imac mmu : sv32 processor : 1 hart : 1 isa : rv32imac mmu : sv32

Similarly, the output of the single-core SoC is as follows, and one core with isa changed is recognized.

/ # cat /proc/cpuinfo processor : 0 hart : 0 isa : rv32imafdc mmu : sv32

Summary

We have successfully created RV32IMAC dual-core SoC and RV32IMAFDC single-core SoC for Sipeed’s Tang Primer and run RISC-V Linux.