Luffca 2022 Wrap-Up

This article is Luffca’s 2022 wrap-up. In 2022, we sensed the potential for the RISC-V Vector Extension and the RISC-V Custom Extension. We are also amazed at the speed of development of NaxRiscv, a RISC-V out-of-order core we have been following.

RISC-V Vector Extension

We have written articles on the RISC-V Vector Extension using PULP’s Ara and 32-bit integer extension Zve32x Vicuna. At this time, it seems that hand-crafted optimizations are needed for high-performance software (kernel).

- Running Auto-Vectorized Program on RISC-V Vector RTL Simulator

- Matrix Multiplication based on the RISC-V Vector Extension

- 1×1 Convolution based on the RISC-V Vector Extension

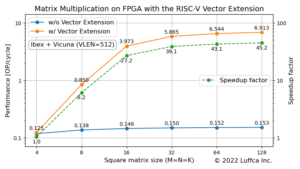

- Matrix Multiplication on FPGA with the RISC-V Vector Extension

RISC-V Custom Extension

Systolic Array

We have written articles on Gemmini being developed at UC Berkeley.

- Running Test Programs on Gemmini Simulators

- Running ResNet-50 on FPGA with Gemmini SoC

- Running ONNX Model on FPGA with Gemmini SoC

SIMD

We have written articles on ML Processor using Google’s CFU Playground.

- Building an ML Processor using CFU Playground (Part 1)

- Building an ML Processor using CFU Playground (Part 2)

- Building an ML Processor using CFU Playground (Part 3)

Tiny Matrix Extension

We have written articles on the Tiny Matrix Extension that speeds up matrix multiplication at low resource cost.

- Tiny Matrix Extension using RISC-V Custom Instructions

- Applying the Tiny Matrix Extension to ML Inference

RISC-V Out-of-Order

We have written articles for NaxRiscv, a RISC-V out-of-order core.

- Benchmarks on RISC-V Out-of-Order Simulator

- Running 32-bit Linux on FPGAs with RISC-V Out-of-Order Core

- Benchmarks on RV64GC RISC-V Out-of-Order Simulator

- Running Debian on FPGA with RISC-V Out-of-Order Core

- TensorFlow Lite for Microcontrollers on RISC-V Out-of-Order Core

We wrote an article about SonicBOOM being developed at UC Berkeley.

RISC-V Multi-Core

We wrote articles for LiteX-VexRiscv and LiteX-Rocket.

- Building an Octa-core 32-bit RISC-V PC on an FPGA board

- Booting RISC-V Debian in LiteX/Rocket on FPGA boards

- Benchmarks in LiteX/Rocket on FPGA boards

- OpenMP on FPGA with RISC-V Multi-Core Processor

Sipeed Tang Primer

We wrote Sipeed Tang Primer articles.