Booting RISC-V Debian in LiteX/Rocket on FPGA boards

We have succeeded in configuring SoCs with 64-bit RISC-V Rocket Chip using LiteX, and booting RISC-V Debian on two FPGA boards, a Qmtech Wukong board and a Digilent Nexys Video.

These SoCs are based on https://github.com/litex-hub/linux-on-litex-rocket etc.

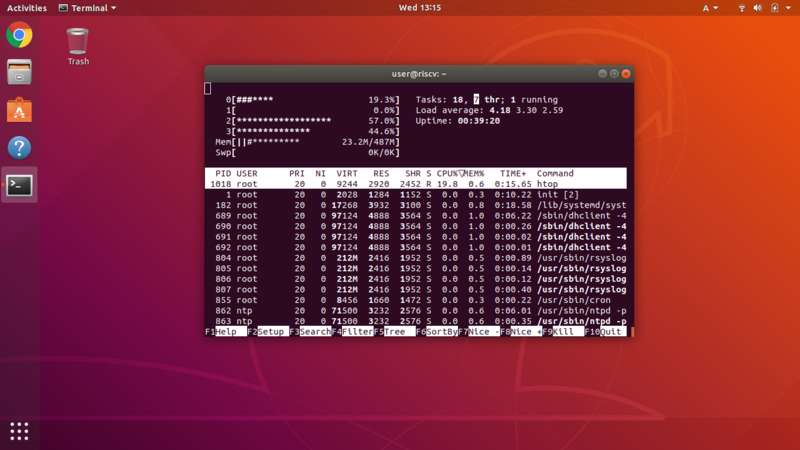

The featured image shows running htop on a terminal UART-connected to the Nexys Video with a quad-core SoC.

LiteX/Rocket

We have modified litex, pythondata-cpu-rocket and linux-on-litex-rocket repositories to add linux4d and full2d as CPU variants for Wukong board with an XC7A100T.

The CPU variants linux4d and full2d mean quad mediumcore and dual bigcore, respectively.

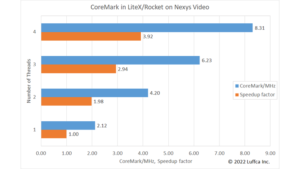

The SoC for Nexys Video with an XC7A200T supports up to quad bigcore full4d.

As shown in the table below, the SoC using LiteX can support twice the number of cores as the SoC using Vivado (vivado-risc-v) introduced in this article, probably because the peripheral IP cores are small.

| FPGA board | Max bigcore | |

|---|---|---|

| vivado-risc-v | LiteX/Rocket | |

| Wukong board | Single | Dual |

| Nexys Video | Dual | Quad |

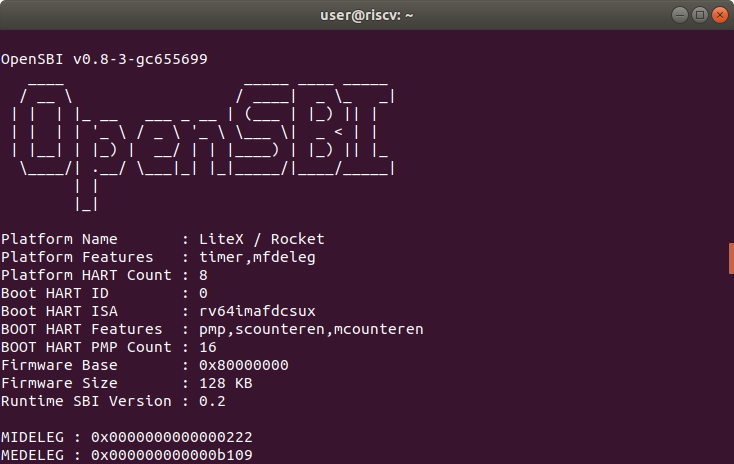

OpenSBI for LiteX/Rocket

We have ported OpenSBI to LiteX/Rocket.

For this reason, we are booting using boot.json instead of boot.bin using Berkeley Boot Loader (BBL).

The boot sequence is as follows.

OpenSBI -> Linux -> rootfs such as Debian

Debian rootfs for LiteX/Rocket

Debian rootfs for LiteX/Rocket uses sysvinit instead of systemd, as described in Boot-Debian-On-Litex-Rocket Step3: Build Debian rootfs.

This time, we booted Debian using the rootfs provided in the releases.

Compared to vivado-risc-v as a Debian environment, we get the impression that the current system is unstable because the RCU stalls at halt etc.

Summary

We have succeeded in configuring SoCs with 64-bit RISC-V Rocket Chip using LiteX, and booting RISC-V Debian on Qmtech Wukong board and Digilent Nexys Video.

The SoCs for Wukong board and Nexys Video using LiteX support up to dual-core and quad-core respectively.