Benchmarks on RISC-V Out-of-Order Simulator

Luffcaでは、RISC-V Out-of-Order CoreのNaxRiscvのシミュレータを作成し、ベンチマークのCoreMarkとDhrystoneを実行しました。

現在のNaxRiscvリポジトリはまだWIPですが、既にシミュレータ上でLinuxが実行できます。また、LiteXに統合されており、FPGAボード用ゲートウェアを作成できます。

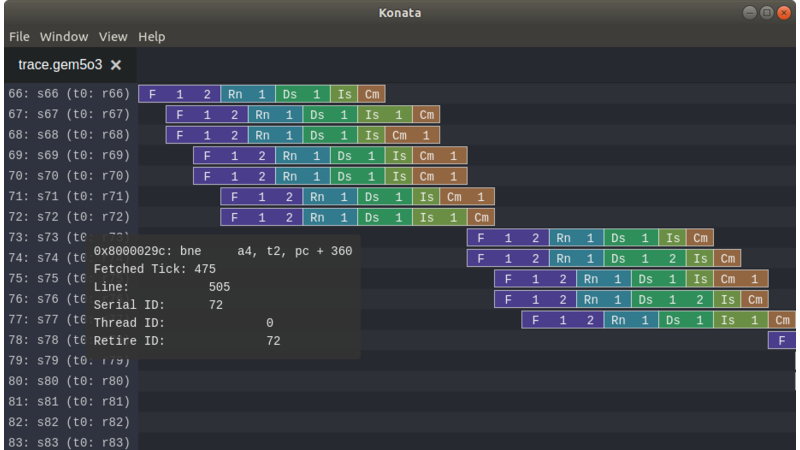

アイキャッチ画像は、シミュレータから出力したログを、命令パイプラインビジュアライザーであるKonataで可視化したものです。

NaxRiscvの関連記事は、こちら。

注:2022/7/16に内容を更新しました。

NaxRiscv

NaxRiscvは、32-bit RISC-V VexRiscvの開発者であるCharles Papon氏が開発を進めているRISC-V Coreです。VexRiscvと同様に、SpinalHDLというハードウェア記述言語で記述されています。

VexRiscvとNaxRiscvの違いは、UCB(カリフォルニア大学バークレイ校)のRocketとBOOM(Berkeley Out-of-Order Machine)のように、インオーダ実行スカラとアウトオブオーダ実行スーパースカラだと思っていましたが、VexRiscvにはなかった64-bit(RV64)対応などの新たな試みが行われています。

NaxRiscvのデフォルトのRV32IMAの性能は、以下のようになっています。

- CoreMark: 5.00 CoreMark/MHz (-O3 and so many more random flags)

- Dhrystone: 2.94 DMIPS/MHz (-O3 -fno-common -fno-inline)

Benchmarks on NaxRiscv Simulator using Verilator

GitHubのNaxRiscvリポジトリには、Verilatorを用いたRV32IMAシミュレータの作成方法の記載があり、CoreMarkやDhrystoneがビルドされているので、再現テストを実施しました。

CoreMark

以下は、CoreMarkを実行したときのコンソール出力を示しています。

$ ./sim/VNaxRiscv32ima --name coremark \ --load-elf $NAXSOFTWARE/baremetal/coremark/build/rv32ima/coremark.elf \ --pass-symbol pass 2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 2001972 Total time (secs): 2001972.000000 Iterations/Sec : 0.000005 Iterations : 10 Compiler version : GCC11.1.0 Compiler flags : -DPERFORMANCE_RUN=1 -march=rv32ima -mabi=ilp32 -mcmodel=medany -Wno-pointer-to-int-cast -Wno-int-to-pointer-cast -I../driver -O3 -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-crossjumping -freorder-blocks-and-partition -DCORE_DEBUG=0 -lgcc -lc -nostartfiles -ffreestanding -Wl,-Bstatic,-T,../common/app.ld,-Map,coremark.map,--print-memory-usage Memory location : STACK seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0xfcaf Correct operation validated. See README.md for run and reporting rules. CoreMark 1.0 : 0.000005 / GCC11.1.0 -DPERFORMANCE_RUN=1 -march=rv32ima -mabi=ilp32 -mcmodel=medany -Wno-pointer-to-int-cast -Wno-int-to-pointer-cast -I../driver -O3 -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-crossjumping -freorder-blocks-and-partition -DCORE_DEBUG=0 -lgcc -lc -nostartfiles -ffreestanding -Wl,-Bstatic,-T,../common/app.ld,-Map,coremark.map,--print-memory-usage / STACK 5.00 Coremark/MHz SUCCESS coremark

シミュレータのCoreMark/MHzは、5.00です。

Dhrystone

以下は、Dhrystoneを実行したときのコンソール出力を示しています。

$ ./sim/VNaxRiscv32ima --name dhrystone \ --load-elf $NAXSOFTWARE/baremetal/dhrystone/build/rv32ima/dhrystone.elf \ --pass-symbol pass Dhrystone Benchmark, Version C, Version 2.2 Program compiled without 'register' attribute Using time(), HZ=12000000 ... Microseconds for one run through Dhrystone: 16 Dhrystones per Second: 62169 User_Time : 965109 Number_Of_Runs : 5000 HZ : 12000000 DMIPS per Mhz: 2.94 SUCCESS dhrystone

シミュレータのDMIPS/MHzは、2.94です。

まとめ

Luffcaでは、Verilatorを用いてRISC-V Out-of-Order CoreのNaxRiscvのシミュレータを作成し、ベンチマークのCoreMarkとDhrystoneを実行しました。