RISC-V Bit-Manipulation ISA-extensions

この記事では、2021年11月にRatifiedされた「RISC-V Bit-Manipulation ISA-extensions」に基づいて、RISC-VのBit-Manipulation拡張の概要を紹介しています。

RISC-VのBit-Manipulation拡張(以下、BitManip拡張)についてネット検索すると、古い内容の記事が多くあります。記事に以下の記載があった場合、内容が古い可能性があります。

- 参照されている仕様がv1.0.0ではない

- Zba、Zbb、Zbc及びZbs以外の拡張が記載されている

- B拡張(またはRVB)と記載されている

BitManip Zba, Zbb, Zbc and Zbs extensions

RatifiedされたBitManip仕様のv1.0.0には、以下の4種類のZb*拡張が記載されています。

- Zba: Address generation instructions

- Zbb: Basic bit-manipulation

- Zbc: Carry-less multiplication

- Zbs: Single-bit instructions

BitManip仕様のv0.93には、10種類のZb*拡張が記載されているので、v1.0.0では、シンプルになっています。

Relationship between misa.B and Zb* extensions

最新の「The RISC-V Instruction Set Manual Volume II: Privileged Architecture」において、misa.Bは”Reserved”となっており、BitManipのZb*拡張と関係はありません。

具体的には、riscv-isa-manualリポジトリの2022年1月26日のコミットc1c77c4において、misa.Bは”Tentatively reserved for Bit-Manipulation extension”から”Reserved”に変更されています。

また、BitManip仕様のv0.93には、8種類のZb*拡張がB拡張に対応することが記載されていますが、v1.0.0では、B拡張との対応を示す記載はありません。

QEMU

この件に関して、QEMUのChangeLog/6.2には、次の記述があります。

RISC-V

- Add Zb[abcs] instruction support

- Remove RVB support

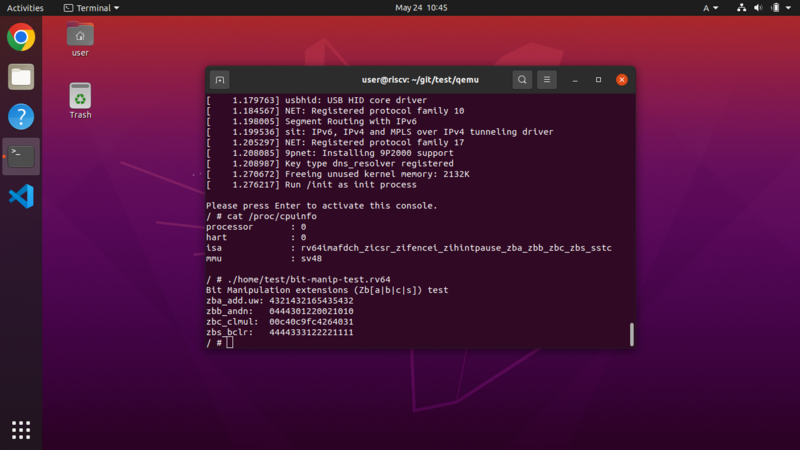

アイキャッチ画像と下記のコンソール出力は、4種類のZb*拡張を有効にしたQEMU 7.2において、cat /proc/cpuinfoを実行した時の結果を表しています。

/ # cat /proc/cpuinfo processor : 0 hart : 0 isa : rv64imafdch_zicsr_zifencei_zihintpause_zba_zbb_zbc_zbs_sstc mmu : sv48

isaの出力を見ると、4種類のZb*拡張に対応するzba_zbb_zbc_zbsを確認できますが、misa.Bに対応するbはありません。

Rocket Chip

また、コミット4ecc497以降のRatifiedされたBitManipのZb*拡張に対応したRISC-V実装であるRocket Chipにおいても、misa.Bは使用されていません。

まとめ

この記事では、RISC-VのBitManip拡張について紹介しました。BitManip拡張についてネット検索すると、古い内容の記事が多くありますので、Ratifiedされた仕様を確認することをおすすめします。