Luffca 2022 Wrap-Up

この記事は、Luffcaの2022年のWrap-Upです。2022年は、RISC-Vベクトル拡張(Vector Extension)とRISC-Vカスタム拡張(Custom Extension)の可能性を感じた一年でした。また、フォローしているRISC-V Out-of-Order CoreのNaxRiscvの開発の速さに驚いています。

RISC-V Vector Extension

PULPのAraと32-bit整数拡張Zve32xのVicunaを用いて、RISC-Vベクトル拡張の記事を書きました。現時点では、性能の高いソフトウェア(カーネル)のために、手作業による最適化が必要そうです。

- Running Auto-Vectorized Program on RISC-V Vector RTL Simulator

- Matrix Multiplication based on the RISC-V Vector Extension

- 1×1 Convolution based on the RISC-V Vector Extension

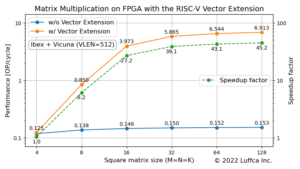

- Matrix Multiplication on FPGA with the RISC-V Vector Extension

RISC-V Custom Extension

Systolic Array

UC Berkeleyで開発されているGemminiの記事を書きました。

- Running Test Programs on Gemmini Simulators

- Running ResNet-50 on FPGA with Gemmini SoC

- Running ONNX Model on FPGA with Gemmini SoC

SIMD

GoogleのCFU Playgroundを用いたML Processorの記事を書きました。

- Building an ML Processor using CFU Playground (Part 1)

- Building an ML Processor using CFU Playground (Part 2)

- Building an ML Processor using CFU Playground (Part 3)

Tiny Matrix Extension

省リソースで行列積演算を高速化するTiny Matrix Extensionの記事を書きました。

- Tiny Matrix Extension using RISC-V Custom Instructions

- Applying the Tiny Matrix Extension to ML Inference

RISC-V Out-of-Order

RISC-V Out-of-Order CoreのNaxRiscvの記事を書きました。

- Benchmarks on RISC-V Out-of-Order Simulator

- Running 32-bit Linux on FPGAs with RISC-V Out-of-Order Core

- Benchmarks on RV64GC RISC-V Out-of-Order Simulator

- Running Debian on FPGA with RISC-V Out-of-Order Core

- TensorFlow Lite for Microcontrollers on RISC-V Out-of-Order Core

UC Berkeleyで開発されているSonicBOOMの記事を書きました。

RISC-V Multi-Core

LiteX-VexRiscvとLiteX-Rocketの記事を書きました。

- Building an Octa-core 32-bit RISC-V PC on an FPGA board

- Booting RISC-V Debian in LiteX/Rocket on FPGA boards

- Benchmarks in LiteX/Rocket on FPGA boards

- OpenMP on FPGA with RISC-V Multi-Core Processor

Sipeed Tang Primer

Sipeed Tang Primerの記事を書きました。